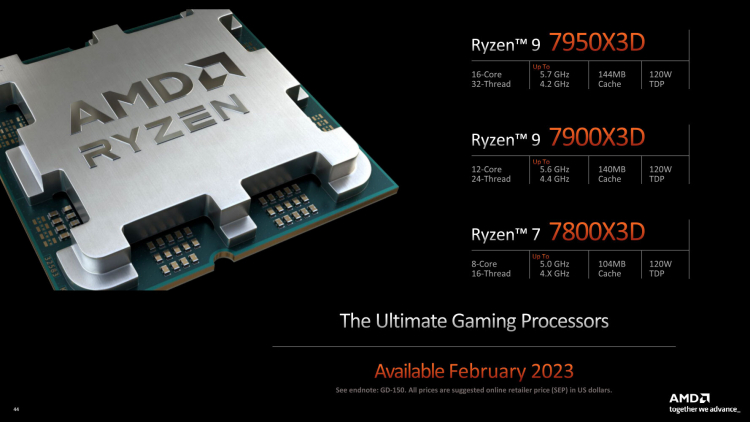

AMD Today announced new high-performance gaming processors Ryzen 7000X3D with increased cache memory. They should go on sale in February. The profile media noticed oddities in the characteristics of new products related to the amount of cache memory itself. It turned out to be smaller than expected.

Image Source: AMD

In particular, TechPowerUp journalists noticed that the 12-core Ryzen 9 7900X3D and the 16-core Ryzen 9 7950X3D, which use two CCD chipsets each, do not have the total amount of cache memory that is expected. In turn, the 8-core Ryzen 7 7800X3D, using a single CCD chiplet, received the expected total cache (L2 + L3) of 104 MB. The younger model has 1 MB of L2 cache for each core, in addition, the processor received 96 MB of L3 cache. The latter consists of 32 MB of cache on the CCD die and an additional 64 MB as a 3D V-Cache layer soldered on top of the CCD chiplet. With the same scheme, for the Ryzen 9 7900X3D and Ryzen 9 7950X3D models equipped with two CCD clusters, the total amount of cache memory in theory should have been 204 and 208 MB, respectively. However, these processors have 140 and 144 MB of shared cache.

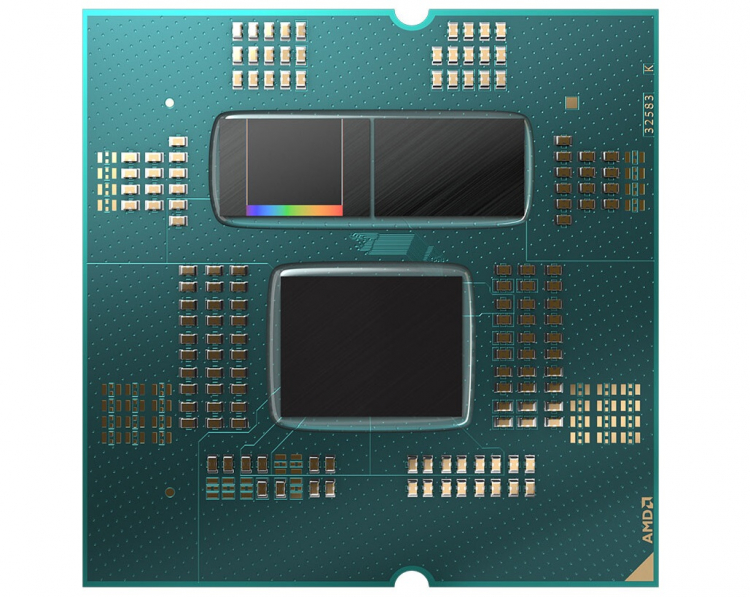

Indirect explanations for this situation were provided by AMD, which published images of processors with two CCD crystals in high resolution. As it turned out, only one of the chiplets has an additional 3D V-Cache cache layer. Its contours are clearly marked with lines in the image below.

From a software standpoint, this asymmetric cache set configuration should not pose any problems. The software market has already managed to adapt to the same Intel and Arm hybrid processors that use completely different types of computing cores on the same substrate. Long before the release of the Intel Alder Lake processors, when the Ryzen 3000 (Matisse) series of chips, the first consumer processors with two CCD chipsets, was released, AMD worked closely with Microsoft to optimize the OS scheduler so that high-intensity computing processes and less parallelized workloads games, for example, were localized to only one of the two CCD dies to minimize latency when communicating with DDR4 memory.

Even before Matisse, AMD and Microsoft were faced with the peculiarities of optimizing multi-threaded workload on processor architectures with two CCX-complexes (such were used in Zen and Zen 2). Then, ideally, the OS scheduler needed to localize the game load on one CCX complex, then distribute it to the second CCX as part of one CCD chiplet, and then redistribute the load to the next CCD chiplet. We managed to solve this by the same method of choosing the preferred CPPC2 core. And that is why AMD highly recommends using the Ryzen Balanced power plan included in the chipset driver in the Windows operating system.

It is highly likely that a similar approach will be used on the 12- and 16-core Ryzen 7000X3D processors, with the gaming workload being handled by the CCD chiplet with 3D V-Cache and the associated workloads (audio stack, networking stack, background services, and etc.) will be executed on the second CCD. In non-gaming workloads that use all processor cores, AMD’s new products will function like any other multi-core processors. At the same time, AMD chips should not have any problems with errors due to the difference in architectures that were first observed in the same Alder Lake processors, since both of their CCD chiplets use the same Zen 4 architecture.

If you notice an error, select it with the mouse and press CTRL + ENTER.