From nanometer to angstrom; the institute predicts an etching fineness of less than 1 nm around 2030.

Last week, the Imec (Institute of micro-electronics and components), unveiled, as part of the event Future Summit in Antwerp, Belgium, its roadmap until 2036 for process nodes and transistor designs. For the fineness of etching, the projections therefore logically include nodes smaller than 1 nm.

First of all, a few words regarding the Imec. Little known to the general public, it is “a Flemish inter-university research institute in micro-electronics and nanotechnology located in Leuven in Belgium”. The institute collaborates with the world’s leading semiconductor manufacturers (TSMC, Intel, Samsung, etc.) and other semiconductor software design companies (Synopsys, Cadence, etc.). It is also a partner of ASML, the leading Dutch company in the manufacture of photolithography machines (EUV scanners); moreover, this occurred during the event.

Samsung: mass production in 3 nm should start this quarter

The era of sub-1 nm in 2030

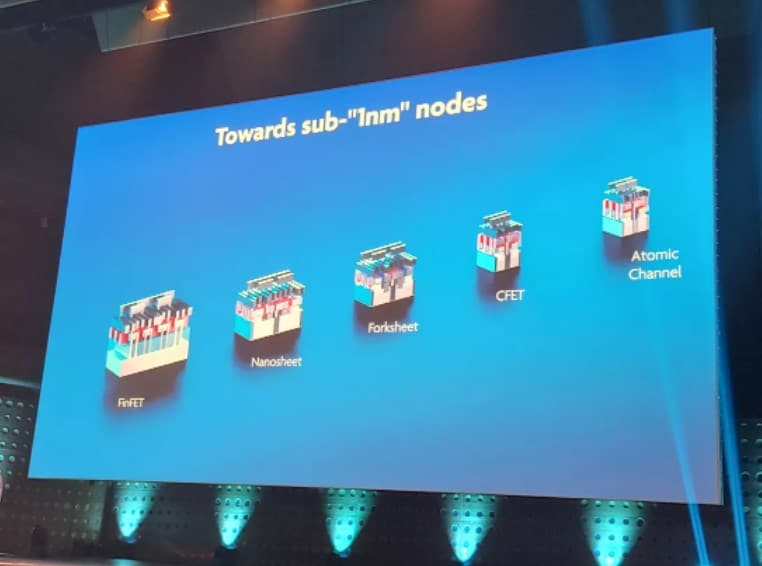

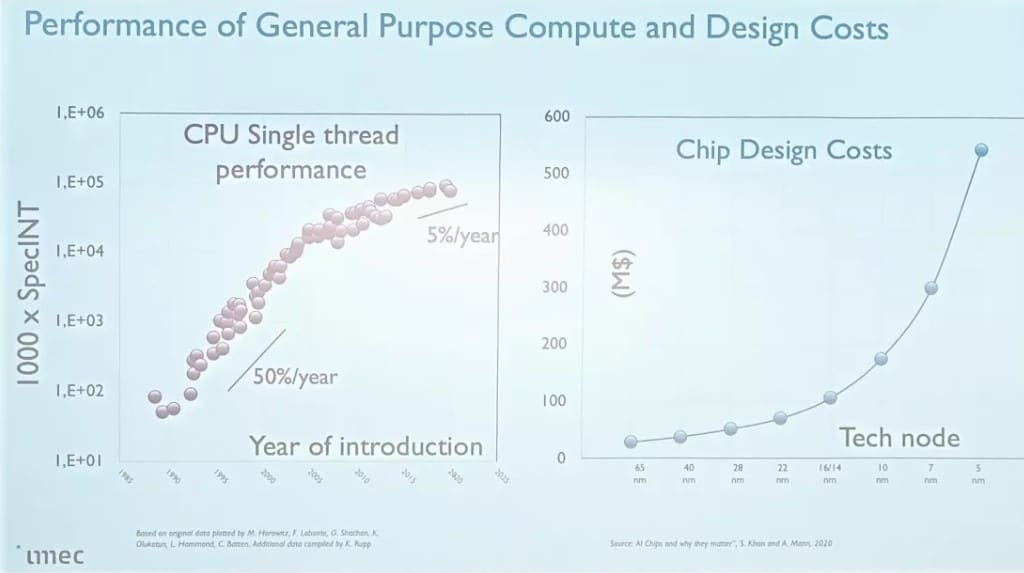

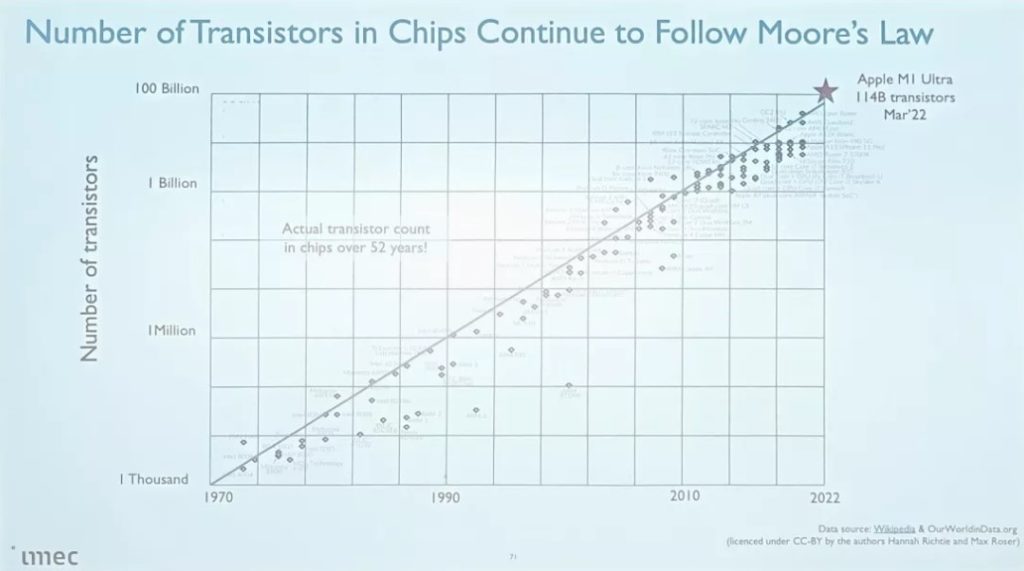

Having made these clarifications, let’s look at the institute’s roadmap. She mentions transistor designs ranging from the now traditional FinFET (down to 3 nm), to so-called GAA designs (Gate All Around), from 2 nm to A7 (seven angstroms; one angstrom is 0.1 nanometer). Next will come new designs for nodes A5, A3 and A2 (CFET – Complementary FET). In terms of timing, the A7 will potentially usher in the sub-1nm era around 2030; it is not guaranteed, however, that chip designers will keep pace, particularly due to exponential costs.

In addition, two slides presented by ASML showed that the standard DUV offers a density of 100 MTr/mm2 (mega-transistor per square millimeter); the current 0.33 NA allows a density of regarding 500 MTr/mm2. Upcoming High NA machines (0.55 NA) will bring it up to around 1000 MTr/mm2.

Do not hesitate to consult the article of our colleagues from Tom’s Hardware US for more information. It contains more slides some of which relate to the design/power challenges that the different nodes will entail.